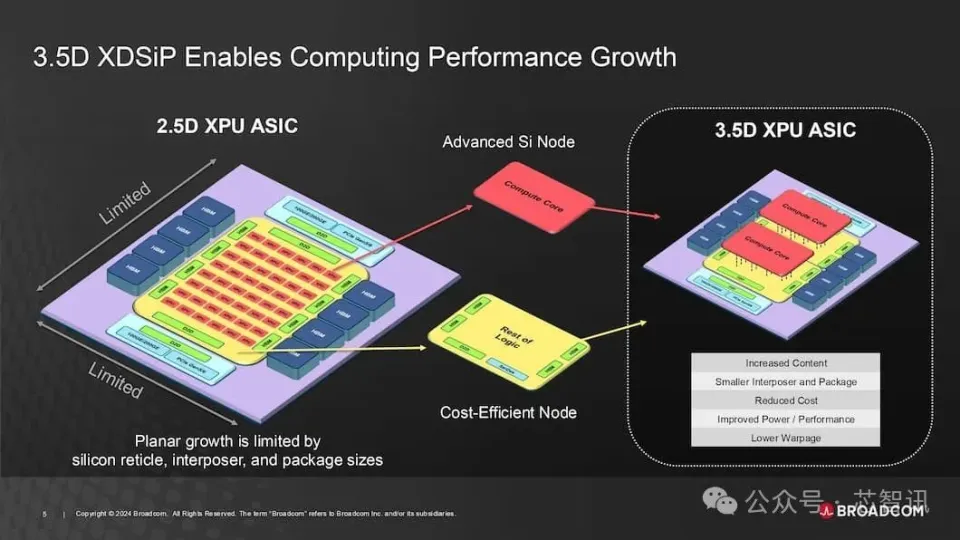

近日,博通推出了3.5D XDSiP(3.5D eXtreme Dimension System in Package)平台,这也是业界首个3.5D面对面(F2F)封装技术,允许集成高达6,000平方毫米的3D堆叠具有 12 个 HBM 模块的硅晶圆可创建系统级封装 (SiP)。预计首款3.5D XDSiP产品将于2026年发布。

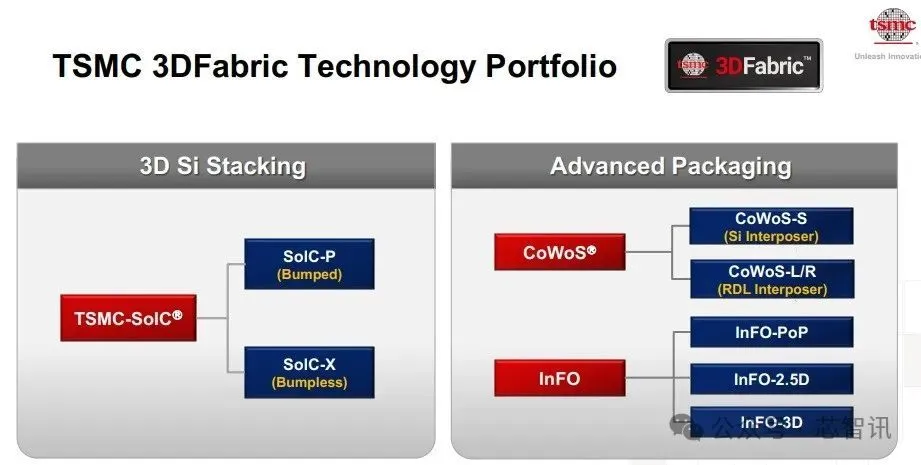

据介绍,博通3.5DXDSiP采用台积电CoWoS-L封装技术,可提供约5.5倍掩模尺寸的封装,使总面积达到4,719平方毫米。它可以包括逻辑IC、最多12个HBM3/HBM4堆栈和其他I/O芯片集成在一起。

为了最大限度地提高性能,Broadcom建议使用分解的计算芯片设计,并使用混合铜键合(HCB)以F2F的方式将一个逻辑芯片堆叠在另一个逻辑芯片上。该方法采用无微凸块(bumpless)混合键合直接连接上下硅芯片的金属层。与依赖硅通孔(TSV)的面对面相比,Broadcom 3D XDSiP 平台的主要优势在于。

博通指出,F2F技术可以将信号连接数量增加7倍并缩短信号路径,同时将芯片间接口的功耗降低90%,减少内部计算、内存和I/O组件之间的延迟时间。 3D堆栈,实现更小的中介层和封装尺寸,从而节省成本并改善封装翘曲问题,为设计团队在上下芯片之间重新分解ASIC架构提供更大的灵活性。

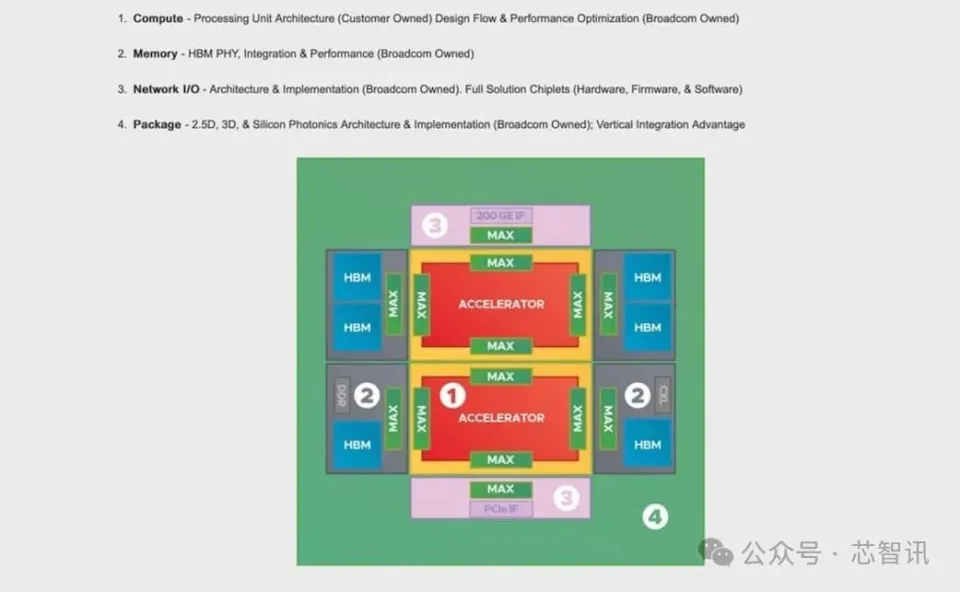

Broadcom高级副总裁兼ASIC产品部总经理Frank Ostojic表示,该公司与客户密切合作,基于台积电和EDA合作伙伴的技术和工具创建了3.5D XDSiP平台。通过垂直堆叠芯片组件,Broadcom 的 3.5D 平台允许芯片设计人员为每个组件匹配适当的工艺,同时缩小中介层和封装尺寸,从而显着提高性能、效率和成本。

Broadcom 的 F2F HCB 技术适用于 3.5D)。由于该平台同时使用2.5D集成和3D堆叠,因此博通将其称为“3.5D”。

台积电业务发展与全球销售高级副总裁兼副联席首席运营官张凯文表示:“台积电和博通在过去几年中紧密合作,将台积电最先进的逻辑工艺和 3D 芯片堆叠技术与Broadcom 的设计专业知识的组合。”

Broadcom 将使用其 3.5D XDSiP 系统级封装平台为具有无限性能需求的公司(例如 Google、Meta 和 OpenAI)设计定制 AI/HPC 处理器和 ASIC。作为该平台的一部分,博通将提供广泛的 IP,包括 HBM PHY、PCIe、GbE、全解决方案小芯片,甚至硅光子,使客户能够专注于其处理器最关键的处理单元架构。

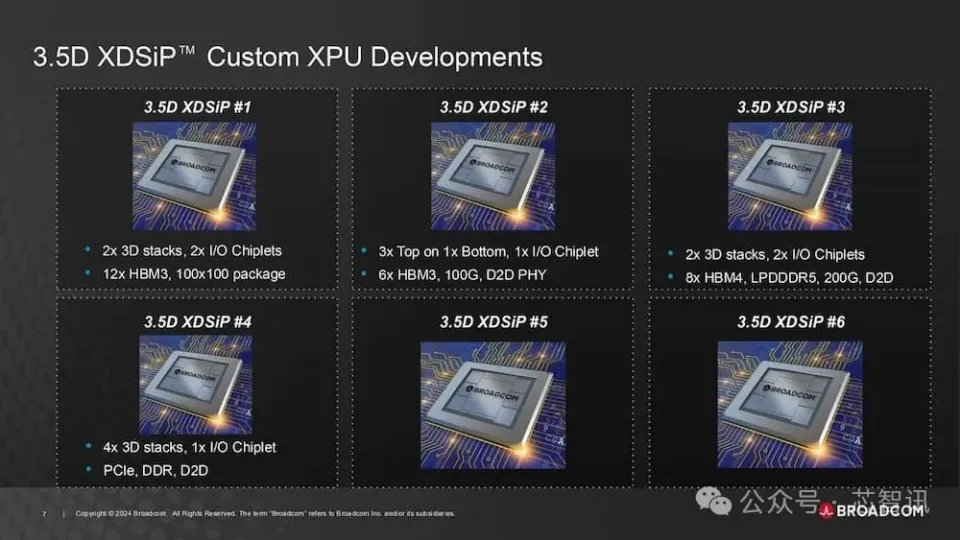

Broadcom的3.5D XDSiP产品集成了由台积电N2(2nm)工艺制造的四个计算芯片、一个I/O芯片和六个HBM模块。该公司还向使用该技术的客户展示了许多不同的设计。

Broadcom目前正在开发五款使用其3.5D技术的产品,其中包括几款来自其主要客户、针对不断增长的AI领域的产品,以及一款将采用Arm ISA和台积电2nm级制程技术的Fujitsu Monaka处理器——针对AI和HPC领域。 Broadcom透露,其3.5D XDSiP产品将于2026年2月开始发货。

富士通高级副总裁兼先进技术开发总监Naoki Shinjo表示,凭借长达十多年的合作关系,富士通和博通已成功将多代高性能计算ASIC推向市场。 Broadcom最新的3.5D平台使富士通下一代基于Arm的2nm处理器FUJITSU-MONAKA实现了高性能、低功耗和低成本。

本文采摘于网络,不代表本站立场,转载联系作者并注明出处:http://mjgaz.cn/fenxiang/273228.html