说起芯片制造,大家知晓制程工艺的重要性。制程工艺是芯片行业的根基。然而,随着半导体工艺日益复杂,其提升空间逐渐变小。同时,人们对于芯片性能的追求从未停止,尤其是在进入新的 AI 时代之后。

这个时候,封装技术的重要性越发明显了。它能够持续提升性能,还为芯片制造带来了极大的灵活性,使得人们可以随心所欲地打造理想的芯片,以满足各种不同的需求。

Intel 是半导体行业的龙头。在半个多世纪的时间里,它一直对封装技术极为重视。并且一直在不断推动封装技术的演化。

最近,Intel 先进系统封装与测试事业部的副总裁兼总经理 Mark Gardner 特意分享了 Intel 在封装技术方面的成果以及他的思考。

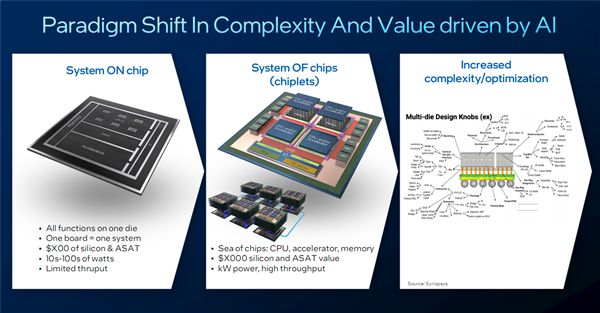

在以往的SoC单芯片时代,封装技术往往不被在意。

近些年 chiplets 芯粒兴起且流行,这使得封装技术变得极为重要,同时芯片的复杂度在不断提升,优化也呈现出指数级的增长态势。

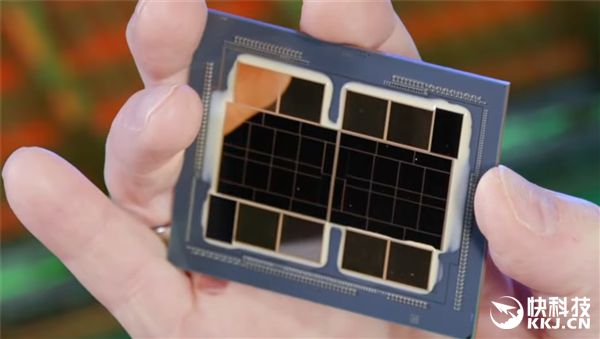

在一个 AI 加速器中,一个封装内会集成多种芯片。这些芯片包括 CPU 计算模块、GPU 加速模块、HBM 高带宽内存以及其他各类 IP。需要以最合理的方式将它们整合在一起,让它们各自发挥出最大性能,同时要实现高带宽、低延迟的互联。

这就让封装技术真正走向前台,成为行业焦点。

提到封装技术,Intel 是人们比较熟悉的。在其悠久的历史进程中,经历了许多的演变。

20 世纪 70 年代微处理器发展初期,使用的是 Wire-Bond 引线键合封装技术。其中包括 QFP 方形扁平封装和 QFN 方形扁平无引脚封装。那时候的芯片较为简单,甚至能够手工丝焊。直到现在,一些简单芯片仍在使用这种封装技术。

90 年代的奔腾处理器采用了倒装键合与陶瓷基板的组合。之后,又发展出了有机基板。同时,还出现了初步的多芯片整合封装。

最近几年,Intel 处理器的封装技术呈现出多点开花的态势。EMIB 2.5D 这种方式不断出现,Foveros 3D 也在涌现,EMIB 3.5D 同样层出不穷,Foveros Direct 3D 也不断出现。并且这些方式经常会混合搭配起来使用,以此来制造更为复杂且强大的芯片。

这些技术的形成并非在短时间内就能完成,而是经过了长期的发展。例如,基于 EMIB 2.5D 的首个产品 Kaby Lake-G 已经投入生产,到现在已经将近十年了。并且,它是唯一一款将 AMD 核显集成在一起的 Intel 处理器。

Intel 近期提出了玻璃基板和玻璃核心。目前这两项仍在推进过程中。计划在本世纪 20 年代的后半期推出,也就是 2025 年到 2030 年之间,将其作为整体平台的一部分。

Intel 认为,玻璃核心的关键在于持续进行扩展。其中包括微凸点技术,还有更大的基板尺寸,以及增强的高速传输等。

在新的形势要求之下,Intel Foundry 代工进行了一些举措。它增加了系统级架构和设计服务,与产品部门展开深度合作,持续提出更为先进且高效的封装技术,然后将这些技术反哺给产品设计与制造。

几年前的数据中心 GPU Max(代号 Ponte Vecchio),使用了 5 种不同制造工艺,封装了 47 个不同模块,耗费了 1000 亿规模的晶体管。

这就是Intel代工完整的先进封装产品组合。

左边是 FCBGA(倒装芯片球栅阵列封装),它有两种不同的版本,分别是 FCBGA 2D 和 FCBGA 2D+。

其中,FCBGA 2D 属于传统的有机 FCBGA 封装。这种封装目前仍在进行量产。它非常适合用于低成本的简单产品,因为这些产品不需要高速 I/O 或者芯片间的高带宽连接。

FCBGA 2D+增添了基板层叠技术。这种技术适合芯片本身不复杂的产品,同时也适合主板连接部分尺寸较大的产品。它能使成本更优,尤其在网络和交换设备领域表现突出。

中间的是嵌入式多芯片互连桥接(EMIB),它有两种版本,分别是 EMIB 2.5D 和 EMIB 3.5D。

EMIB 2.5D 可用于单层芯片。它也能够进行 HBM 堆叠。芯片通过基板上的微型硅桥进行连接。这种连接方式适合高密度的芯片间连接。它在 AI 和 HPC 领域具有显著优势。

EMIB 3.5D 采用了 3D 堆叠技术,将芯片堆叠在一个有源或无源基板上,例如中介层。这种方式更加灵活,像某些对互联距离和延迟有高要求的 IP 模块,由于不适合水平连接,所以需要进行垂直堆叠。

最右边的是 Foveros,它可以被细分为两个版本,分别是 Foveros 2.5D 和 Foveros 3D 以及 Foveros Direct 3D。

其中,Foveros 2.5D/3D 与 EMIB 2.5D/3.5D 有相似之处,它们都可以和其他中介层技术相结合使用,不过 3D 更侧重于垂直堆叠。它们的不同之处在于,Foveros 采用基于焊料的方式来连接芯片与晶圆,而非基底连接,这种方式适合高速 I/O 与较小芯片组分离的设计。

值得一提的是,EMIB 2.5D 能够顺利地转换为 EMIB 3.5D。能够将已定义、设计和制造好的 GPU 或者 HBM 芯片利用 EMIB 2.5D 技术进行集成,接着无需对其设计进行任何更改,就可以将其再次集成到 EMIB 3.5D 封装的单元上。

Foveros Direct 技术采用铜 - 铜直接键合,而非焊料与焊料的连接。这样就能实现最高的带宽,同时也能达到最低的功耗。

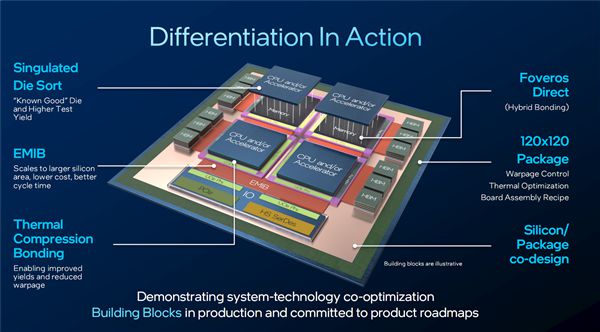

事实上,这些封装技术并非独立存在,并非单一存在且彼此排斥。尤其在 AI 和 HPC 产品中,经常会结合使用多种技术,比如可能会采用 Foveros Direct 3D,并且会与 HBM 连接,最终形成 EMIB 3.5D 封装。

这些封装技术已经不再仅仅停留在路线图中,而是成为了现实。它们已经投入商业使用,其中有些技术已经使用了多年,并且涉及到了多代产品。

不同的芯片如何选择最适合的封装技术是个难题。例如,为何说 EMIB 是 AI 芯片的理想选择?它有哪些优势?上边这张图能够给出答案。

EMIB 2.5D 相较于硅中介层(Si Int)、重布线层(RDL)中介层等其他 2.5D 封装技术,其第一个优势在于成本最低。

从图中可知,EMIB 桥接是一种硅片,它的尺寸非常小。这种硅片能够高效地利用晶圆面积,其利用率常常能超过 90%。然而,其他中介层技术由于是大型封装结构,会导致很大的晶圆面积被浪费,其利用率可能仅有 60%左右。

当扩展到更大面积的芯片复合体时,EMIB 的成本优势会有显著的增长,并且这种增长呈现出指数级的态势。

第二个优势是具有良好的良品率,第三个优势是拥有最快的生产周期,并且这两个优势紧密相连。

它不需要晶圆级封装,也就是芯片对晶圆(Chip-on-Wafer)这种方式。这种方式包含将顶层芯片附着到晶圆上,且涉及模具、凸点等多个工艺步骤。这样不但提升了良率损失的风险,所需的步骤和时间也更久,通常得多花费几个星期的时间。

如今市场形势变化多端,若能提前几周获取样片,并且对其进行测试和验证,这对客户而言是极具吸引力的。

硅桥嵌入基板的特性带来了第四个优势,这种特性能够匹配更大的遮罩(Reticle)。

制造基板时,是在一个大的方形面板上进行操作。这样做能够大幅提高面板的利用率。基板的尺寸与面板相匹配,其可扩展性更好,能够适应大型复杂封装的需求。

AI 芯片都希望在一个封装中集成更多的 HBM 并容纳更多的工作负载。而 EMIB 2.5D 可以很好地满足这一需求。

第五个优势是多样化的供应链支持。

EMIB 为客户提供了较多的灵活性,也为客户提供了更多的选择权。它已经被应用了将近十年,在这期间积累了成熟的技术,并且拥有成熟的供应链。

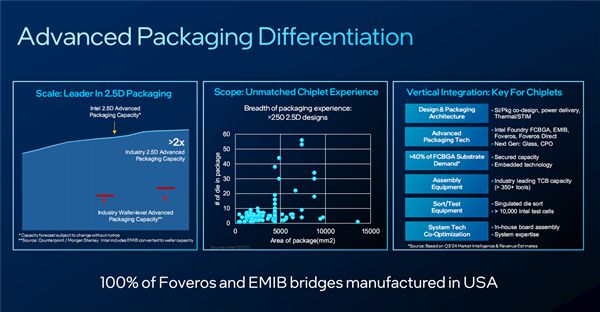

Intel一直是2.5D封装的领导者,拥有庞大无比的产能。

第三方数据表明,Intel EMIB 2.5D 封装的产能以及 Foveros 2.5D 封装的产能,与行业晶圆级先进封装的产能相比较,在规模上超出 2 倍还多。

因此,客户不管有多急迫,也不管有多么大规模的产能需求,Intel 都能够轻松地予以满足。

Intel 迄今已完成 250 多个 2.5D 封装设计项目。这些项目中,既有 Intel 自身的产品,也有第三方客户的产品。并且涵盖了几乎所有的领域。

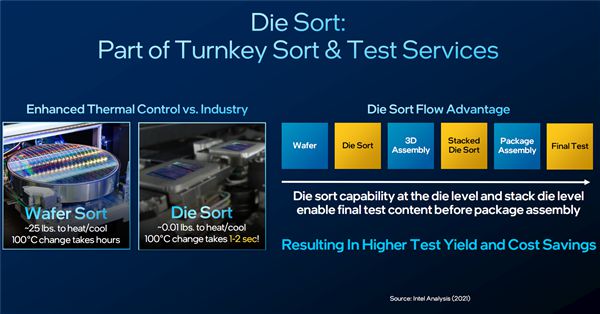

对于复杂封装而言,测试和验证也是至关重要的一环。

当一颗芯片内封装了四五十个不同模块时,只要其中有一个不合格,就会致使整体报废。因为哪怕只有一个不合格的模块,也足以引发整体的报废情况。

所以,不能等整颗芯片封装完毕后才开始进行测试,因为那样风险会非常高。

Intel 开发了一种技术名为“裸片测试”(Die Sort)。它把一整块晶圆切割成一个个单独的裸片。这些裸片在组装到基板上之前就会被进行分类和测试。

裸片面积很小,所以加热和冷却都能做到非常快速且精确,仅需一两秒就能实现约 100 摄氏度的变化。

这种热控制很精确,它让过去只能在最终测试阶段进行的工作,提前到了裸片测试阶段。这样就能更早地发现缺陷,并且能够及时纠正,进而显著提高了生产效率与良品率。

裸片在基板上堆叠完毕后,在整体封装完成之前,Intel 能够进行一次“堆叠芯片测试”(Stacked Die Sort),以此来进一步对功能和性能的完整性进行测试与验证。

以一颗复杂 AI 加速器为例,它包含多个不同模块,且采用了 3D 堆叠技术。接下来看一下 Intel 的多种封装、测试技术是怎样协同工作的。

首先,EMIB 有替代传统大型、昂贵中介层或桥接器的作用。这样一来,能够降低成本,并且还能提高生产效率以及良品率。

EMIB 有一个关键之处,即热压键合(Thermal Compression Bonding),这种方式能够使裸片更高效地组装到基板上。

EIMB 能够与 Foveros Direct 技术相结合,其中包含 3D 混合键合(3D Hybrid Bonding),从而获得最为优化的封装组合。

Intel 目前正在开发 120×120 毫米的封装尺寸,接下来是超大封装。预计未来一两年该封装尺寸就能量产,并且 Intel 不会仅停留在这一尺寸上。

不过,封装尺寸越来越大的话,很容易出现翘曲问题。NVIDIA Blackwell 就遭遇了这样的情况,它很不幸地遇到了明显的翘曲问题。

Intel为此引入了一系列创新技术,并且将这些技术与热优化相结合,这样一来,即便处于翘曲的情况下,也依然能够进行板级封装。

硅片与封装协同设计,即 Silicon Package Co-Design,还有模拟裸片测试,也就是 Simulated Die Sort,二者共同构建了差异化的 AI 产品。

Intel 从独立之后开始代工,已经对策略进行了调整,以此能够提供更灵活的代工服务。

客户能够仅挑选 Intel 进行代工的 EMIB 技术或者封装服务,而芯片部分则交由其他代工厂来处理。

客户能够只要求 Intel 代工的裸片测试方案,并且同样可以单独提供该方案。

Intel 代工在晶圆制造方面采取了相同策略,它能够根据客户需求而灵活变动,从而提供最具价值的服务。

事实上,Intel 与台积电、三星等其他代工厂存在竞争关系。同时,它们一直有着密切合作。它们制定了互相兼容的设计规则。这样做是为了确保其他代工厂生产的晶圆能够兼容 Intel 代工的封装技术。通过这种方式,为客户提供了更多选择,让客户能够自由地综合使用不同代工的技术。

Intel 透露,AWS 亚马逊云成为了 Intel 代工的封装服务客户。Intel 还透露,思科也成为了 Intel 代工的封装服务客户。这些合作主要集中在数据中心服务器领域以及 AI 加速器产品领域。

本文采摘于网络,不代表本站立场,转载联系作者并注明出处:http://mjgaz.cn/fenxiang/275188.html